Huawei has filed a patent for a quad-chiplet design that may be used for its next-generation AI accelerator known as the Ascend 910D. Huawei’s quad-chiplet design certainly mimics Nvidia’s approach for its quad-chiplet Rubin Ultra, but there is one more interesting thing in that patent around Huawei’s plans for its advanced chip packaging — it appears that Huawei is developing techniques that could rival market-leader TSMC’s advanced packaging tech. This could eventually enable the company to sidestep US sanctions and catch up to Nvidia’s AI GPU performance more quickly.

That detail is, of course, in the patent that describes how a quad-chiplet processor could be made. While we cannot say for sure that it is the Ascend 910D, we can certainly connect some dots and make an assumption about the possible part (even though the patent, of course, does not indicate that). It also aligns with current chip industry insider chatter that suggests a quad-chiplet 910D is in the works.

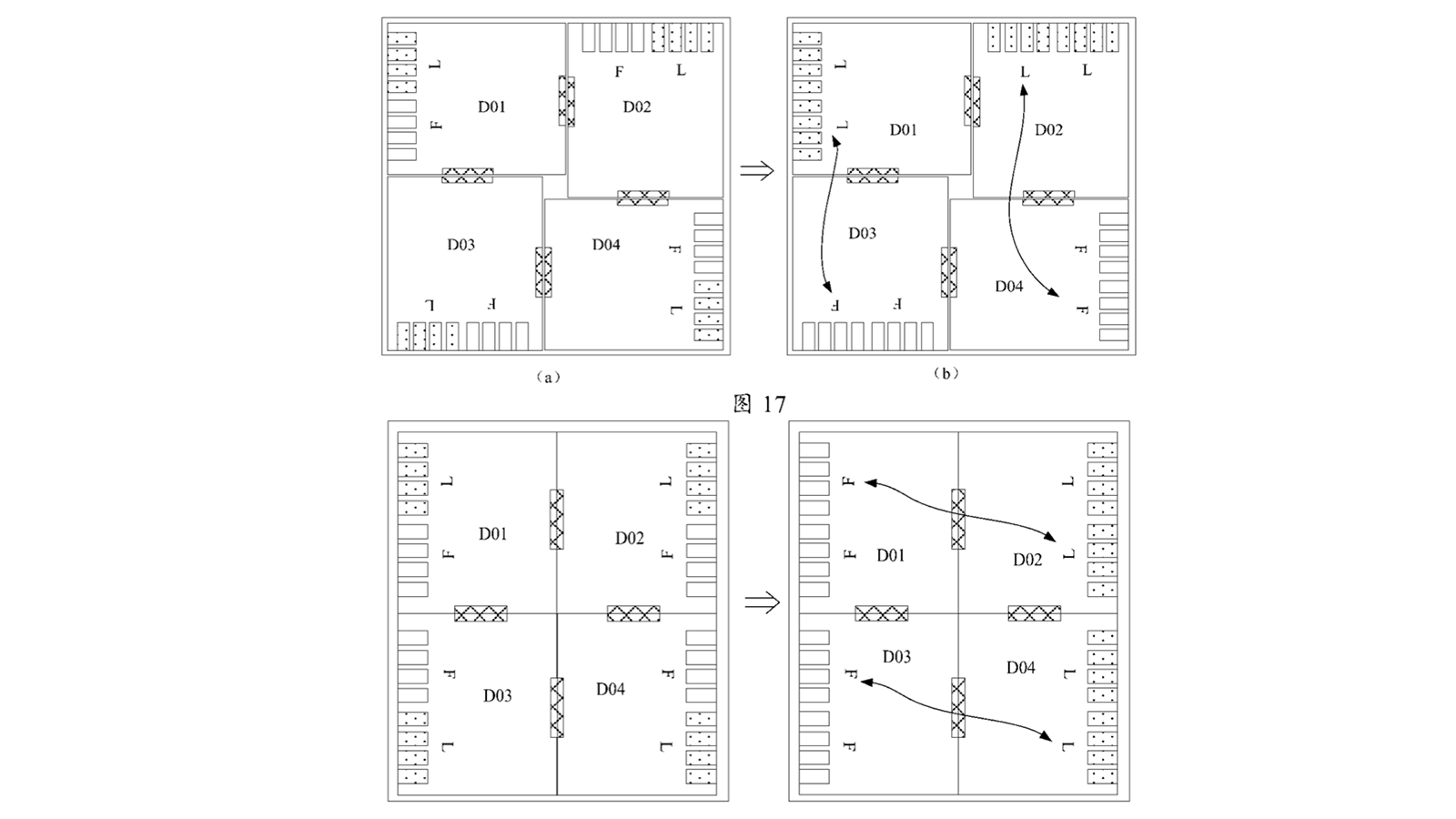

Perhaps a more interesting part about the rumored Ascend 910D is the interconnection between the compute chiplets, which appear like bridges (TSMC’s CoWoS-L or Intel’s EMIB with Foveros 3D) rather than ‘just’ an interposer (at least from the patent point of view). Meanwhile, a processor designed for AI training ought to be accompanied by a bunch of HBM-class memory modules, and these modules may use an interposer-class interconnection.

While SMIC and Huawei are certainly behind in terms of lithography, they might be on par with TSMC in terms of packaging. That would be a key development that would help China sidestep the impact of US export restrictions that bar access to leading-edge chip manufacturing. Instead, Chinese companies could simply use advanced packaging to tie together multiple chiplets using older process node technology, enabling them to match, or at least come close to, the performance of chips made with leading-edge process nodes.

Here comes some difficult math that we cannot confirm: The single-chiplet Ascend 910B is believed to have a die size of 665 mm², so we can quadruple that to 2,660 mm² in the case of the 910D (though keep in mind). As every 910B carries four HBM chiplets (let us assume they are 85 mm²), four of them will increase the HBM memory stack count to 16, leading DRAM’s footprint to a whopping 1,366 mm².

This leads us into speculative territory, but producing an Ascend 910D processor would require at least a total silicon area of 4,020 mm². By TSMC’s standards, this counts as five EUV reticle sizes (858 mm²), a type of packaging that the company plans to introduce for volume production in 2026.

When we first heard rumors about Huawei’s quad-chiplet Ascend 910D accelerator for AI back in April, we took it with a spoon of salt and a pinch of pepper back then. However, the rumor is now gaining traction, and Huawei is indeed working on a four-die processor called Ascend 910D, which is projected to surpass Nvidia’s H100 in per-GPU-package performance. We should still take it with a grain of salt (at least not a whole spoonful of it), as not all patent applications ultimately result in actual products.

In addition to the 910D, Huawei is reportedly working on a future processor under the Ascend 920 moniker, but that part was supposed to compete against Nvidia’s H20. This naming scheme is, of course, illogical, but as there might be some merit behind that report, we should also keep this in mind.

Follow Tom’s Hardware on Google News to get our up-to-date news, analysis, and reviews in your feeds. Make sure to click the Follow button.